TMS320C6657CZHA IC DSP 수정/부동 소수점 625FCBGA

제품 매개변수

설명

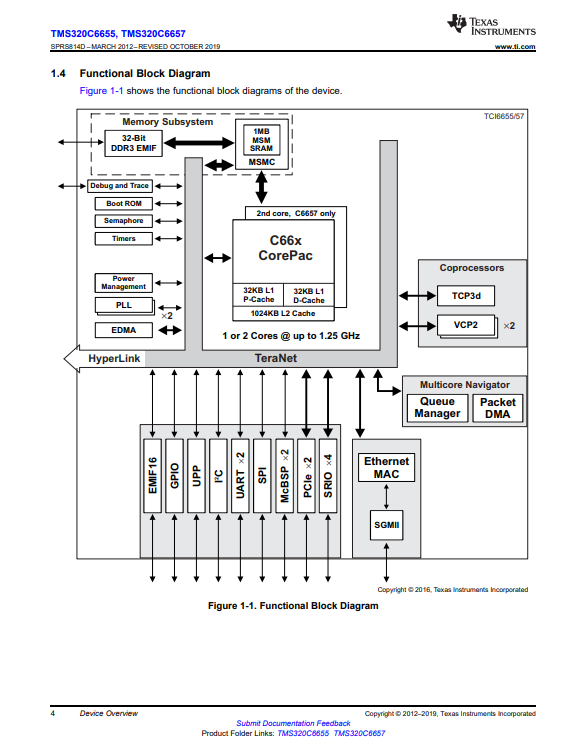

TI의 KeyStone 아키텍처는 다양한 하위 시스템(C66x 코어, 메모리 하위 시스템, 주변 장치 및 가속기)을 통합하는 프로그래밍 가능 플랫폼을 제공하고 다양한 DSP 리소스가 효율적이고 원활하게 작동할 수 있도록 장치 내 및 장치 간 통신을 최대화하기 위해 몇 가지 혁신적인 구성 요소와 기술을 사용합니다.이 아키텍처의 중심에는 다양한 장치 구성 요소 간의 효율적인 데이터 관리를 가능하게 하는 Multicore Navigator와 같은 핵심 구성 요소가 있습니다.TeraNet은 빠르고 경합 없는 내부 데이터 이동을 가능하게 하는 비차단 스위치 패브릭입니다.멀티코어 공유 메모리 컨트롤러를 사용하면 스위치 패브릭 용량을 사용하지 않고도 공유 및 외부 메모리에 직접 액세스할 수 있습니다.고정 소수점 사용을 위해 C66x 코어는 C64x+ 코어의 MAC(Multiply Accumulate) 기능의 4배입니다.또한 C66x 코어는 부동 소수점 기능을 통합하고 코어당 원시 계산 성능은 업계 최고의 코어당 40GMACS 및 코어당 20GFLOPS(@1.25GHz 작동 주파수)입니다.C66x 코어는 주기당 8개의 단정밀도 부동 소수점 MAC 연산을 실행할 수 있고 배정밀도 및 혼합 정밀도 연산을 수행할 수 있으며 IEEE 754를 준수합니다.C66x 코어는 부동 소수점 및 벡터 수학 지향 처리를 목표로 하는 90개의 새로운 명령(C64x+ 코어와 비교)을 통합합니다.이러한 개선 사항은 신호 처리, 수학 및 이미지 획득 기능에 사용되는 널리 사용되는 DSP 커널에서 상당한 성능 향상을 가져옵니다.C66x 코어는 TI의 이전 세대 C6000 고정 및 부동 소수점 DSP 코어와 역방향 코드 호환이 가능하여 더 빠른 하드웨어로 마이그레이션하는 애플리케이션을 위해 소프트웨어 이식성과 단축된 소프트웨어 개발 주기를 보장합니다.C665x DSP는 많은 양의 온칩 메모리를 통합합니다.32KB의 L1 프로그램 및 데이터 캐시 외에도 1024KB의 전용 메모리를 매핑된 RAM 또는 캐시로 구성할 수 있습니다.또한 이 장치는 공유 L2 SRAM 및/또는 공유 L3 SRAM으로 사용할 수 있는 1024KB의 멀티코어 공유 메모리를 통합합니다.모든 L2 메모리는 오류 감지 및 오류 수정을 통합합니다.외부 메모리에 대한 빠른 액세스를 위해 이 장치에는 1333MHz의 속도로 실행되는 32비트 DDR-3 외부 메모리 인터페이스(EMIF)가 포함되어 있으며 ECC DRAM을 지원합니다.

| 명세서: | |

| 기인하다 | 값 |

| 범주 | 집적 회로(IC) |

| 임베디드 - DSP(디지털 신호 프로세서) | |

| 제조업체 | 텍사스 인스트루먼트 |

| 시리즈 | TMS320C66x |

| 패키지 | 쟁반 |

| 부품 상태 | 활동적인 |

| 유형 | 고정/부동 소수점 |

| 상호 작용 | DDR3, EBI/EMI, 이더넷, McBSP, PCIe, I²C, SPI, UART, UPP |

| 클록 속도 | 1GHz |

| 비 휘발성 기억 장치 | 롬(128kB) |

| 온칩 RAM | 2.06MB |

| 전압 - I/O | 1.0V, 1.5V, 1.8V |

| 전압 - 코어 | 1.00V |

| 작동 온도 | -40°C ~ 100°C(TC) |

| 장착 유형 | 표면 실장 |

| 패키지/케이스 | 625-BFBGA, FCBGA |

| 공급자 장치 패키지 | 625-FCBGA(21x21) |

| 기본 제품 번호 | TMS320 |

관련된제품

-

전화

-

이메일

-

스카이프

-

왓츠앱

왓츠앱